难怪诺贝尔科学奖开挂,日企新技术令人惊叹

日本不仅获得31个诺贝尔奖,其76项半导体材料垄断全球市场。大日本印刷突破1.4nm模板技术,支持佳能纳米压印装置,耗电仅EUV光刻机1/10,成本大幅降低,适用于AI、自动驾驶芯片。台积电、三星计划量产,中国半导体落后,可趁禁售窗口合作引入,实现先进制程弯道超车,补齐7nm短板。

在两个月前的2025年度诺贝尔奖自然科学奖项颁布新闻发布会上,日本又增添了两名诺贝尔奖得主:一个是荣获生理学/医学奖的大阪大学教授坂口志文,另一个是荣获化学奖的京都大学教授北川进。

虽然一年获得两个诺贝尔科学奖已经令囊中羞涩的我们羡慕不已,但更令人惊叹的是,截至2025年,日本获得的诺贝尔奖中,2000年后的25年里,日本获得了22个诺贝尔科学奖,成为获得诺奖最多的非欧美国家。

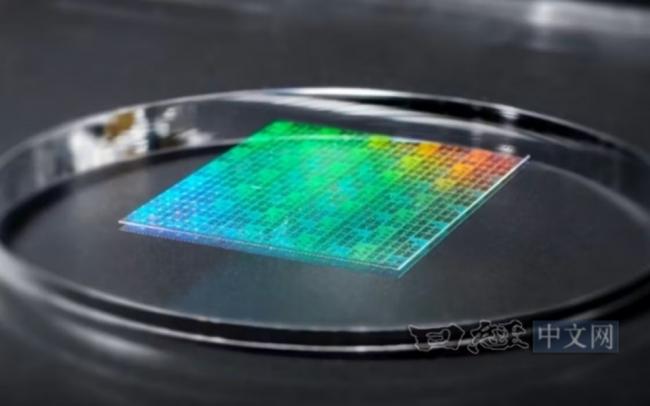

日本在半导体材料和设备领域的技术积累,推动日企砥砺前行,不断实现突破与超越。最近,日企又在先进半导体核心构件方面取得了重大突破。

12月10日,《日经亚洲》报道称,大日本印刷(DNP)开发出了能以十分之一的耗电量生产先进半导体的技术。将面向佳能生产的新方式制造装置,于2027年量产可支持新一代1.4纳米(1纳米为十亿分之一米)产品的核心构件。该技术的出现,让人工智能(AI)半导体的制造成本有大幅降低的可能性。

目前,要量产最先进的半导体,需要使用全球只有荷兰阿斯麦控股(ASML Holdings)生产的极紫外(EUV)光刻机。在晶圆(基板)上绘制电路的“光刻工序”占半导体总制造成本的3至5成。电路越精细,光刻次数就越多,耗电量也随之增加。一台EUV光刻机的价格为300亿日元左右,给半导体厂商带来沉重的投资负担。

而佳能的“纳米压印(Nanoimprint )”制造装置,采用类似盖印章的方式在晶圆上制作电路。大日本印刷开发出了相当于精细印章的电路原版“模板(template)” ,最高可用于1.4纳米制程。此前该技术无法支持2纳米等先进半导体的制造。

制作模板时,需要使用光刻技术。此次大日本印刷重新筛选了材料并调整设置条件,还采用了可使半导体电路密度翻倍的“双重图形化(Double Patterning)”技术。

从2023年开始,佳能便销售与EUV完全不同的纳米压印装置。与EUV光刻机需要使用强光源来转印电路图案需要消耗更多电能相比,纳米压印装置耗电量更低。预计纳米压印装置单台设备的价格为3-5千万美元,销售价格仅为EUV光刻机的六分之一至四分之一。

不过,由于是直接接触模板来绘制电路,这让佳能的纳米压印装置对环境和工艺的要求更高。因为一旦混入杂质,压印电路就容易出现缺陷,良品率就会降低。该工艺同时还面临需要提高处理速度等课题。因此,习惯于使用EUV的芯片制造企业,目前仅存储器大型制造商铠侠控股等引入这种装置,目前还在用于验证用途,尚未在量产线中采用。

更先进的1.4纳米半导体,将主要用于AI数据中心及自动驾驶领域,发挥智能设备大脑的关键作用。全球最大的芯片制造代工企业台积电(TSMC),计划2028年开始量产1.4纳米半导体,韩国的三星电子则计划2027年开始量产1.4纳米芯片。目前,两家企业都表示对纳米压印装置感兴趣。

不过,因为各企业的现有的半导体工厂,均按照已经使用的EUV光刻机为前提设计,而采用纳米压印装置的门槛较高。因此他们只能在新建半导体制造工厂时才能引进这种装置,并按该装置的要求设计对环境要求更高的厂房。这导致佳能纳米压印装置的推广较为缓慢。

过去,佳能和尼康两家日本企业在光刻机市场占据了超过一半的全球份额。但阿斯麦在制程精细化竞争中取得了胜利,目前占据了全球9成市场。如果未来纳米压印装置市场扩大,日本企业有望东山再起。大日本印刷等材料厂商也有望入局。富士胶片控股已表示将通过在绘制电路时涂在晶圆上的材料来涉足这一市场。

佳能已于2024年向美国得克萨斯州及英特尔等半导体企业参与的官民合作组织“Texas Institute for Electronics(得克萨斯州电子研究所)”首次提供纳米压印装置。能否与EUV光刻机形成共享市场的格局,将成为备受关注的焦点。

目前中国公开量产的半导体最先进制程为中芯国际采用DUV多重曝光技术,能在14纳米平台上实现等效7纳米性能的N+1工艺实现的7纳米,而且,良品率很低,产能有限,成本极高。如果我们看到有人说突破了5纳米甚至3纳米,切记,那一定是无法验证的胡编乱造的。

如果我们的半导体大厂能够与大日本印刷和佳能合作,利用半导体压印装置还未被美国列入禁售目录的机会窗口引入其1.4纳米的压印装置,可能真的能够帮助我们在半导体制造领域实现弯道超车,补齐我们在先进制程芯片方面的短板。